半导体设备产业全景(一)

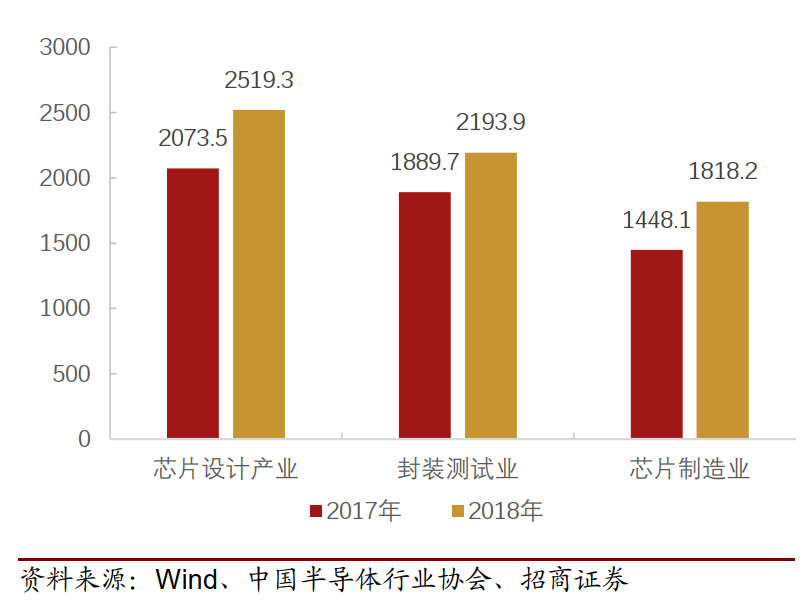

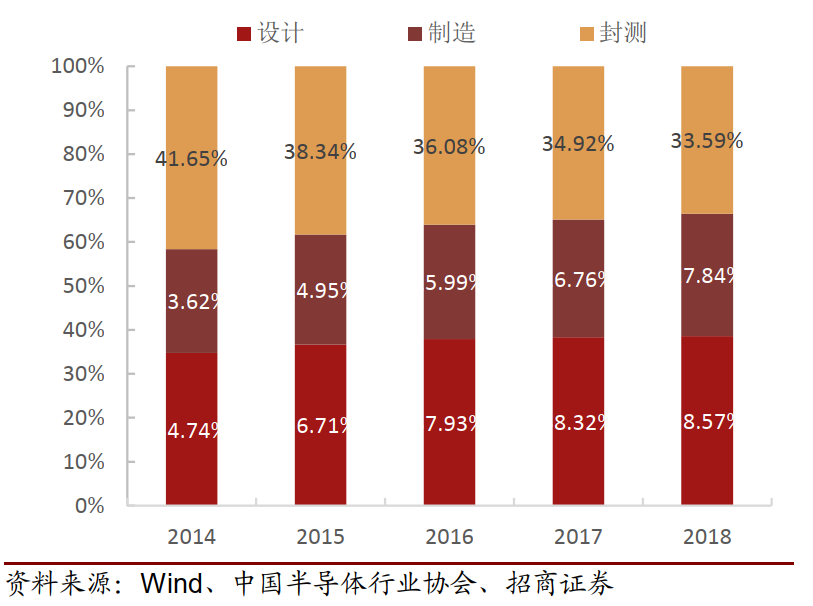

2018年我国集成电路设计、制造和封测行业产值规模约是 1.4 : 1 : 1.2,其中设计业产值在2016年反超封测业。设计业 1999-2016 年年均增长率 45%,2016年发生了巨大变化,在集成电路产业链各环节中,芯片设计业总规模超过制造和封测位列第一(设计占比约 38%),成为第一大产业,长期以来设计业疲弱的情况得到扭转,产业发生了质的变化,设计业在长三角、珠三角、环渤海和中西部地区分布集中,国内前十大芯片设计企业都是本土企业,几年来产品自给率增长不少,2012 年仅为 13.3%,而 2016年达到 26.6%,发展强劲,由此也催促IC制造和封测行业提升自给率,而制造和封测行业远比设计依赖设备,因此半导体设备逐步进口替代是重中之重。

图1:集成电路产业链规模( 亿元)

图2:中国 IC 产业结构变化

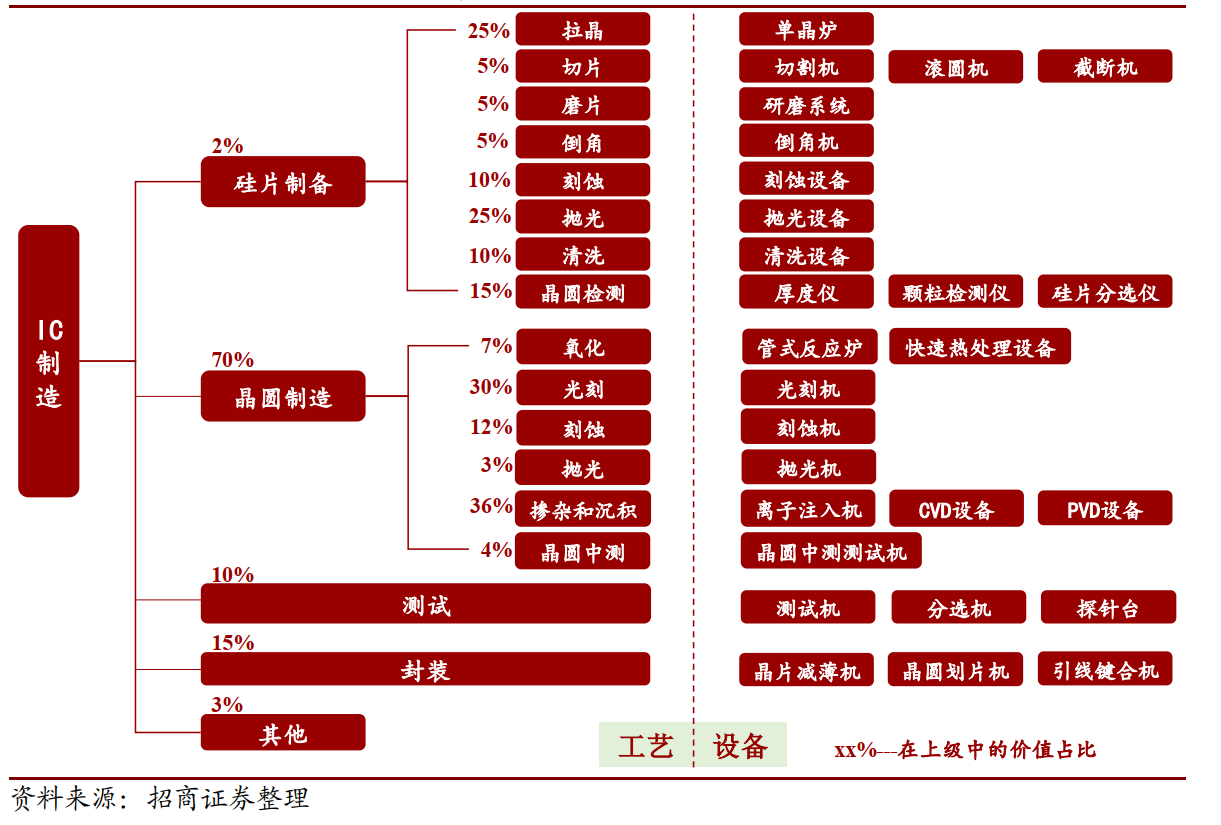

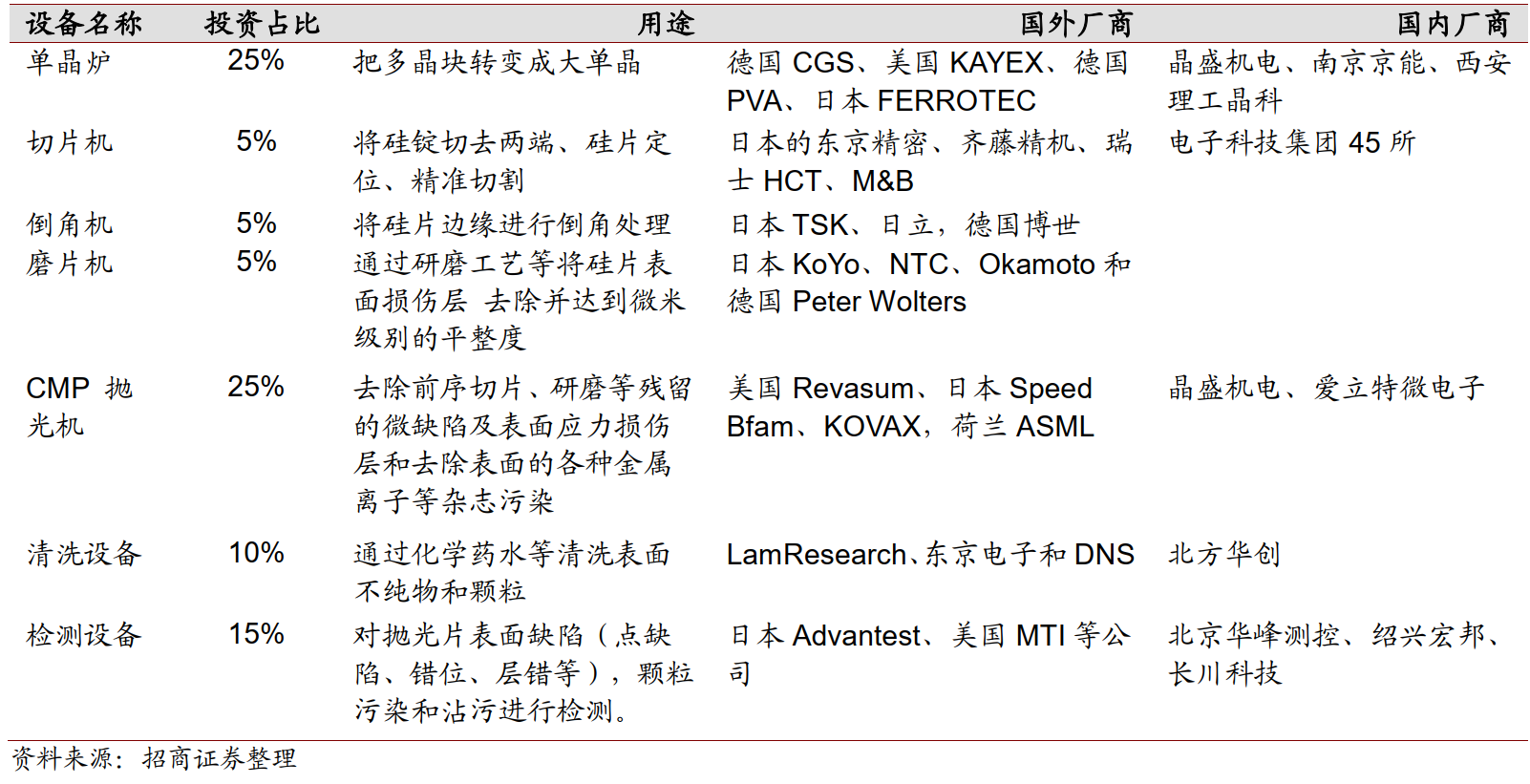

为了便于研究 IC 制造和封测行业对设备的需求,可以将封测也并入 IC 制造工序,也就是当芯片封装测试后才算制造完成,由此可以将广义的 IC 制造分为三大阶段:硅片制备—晶圆制造—晶圆封测。

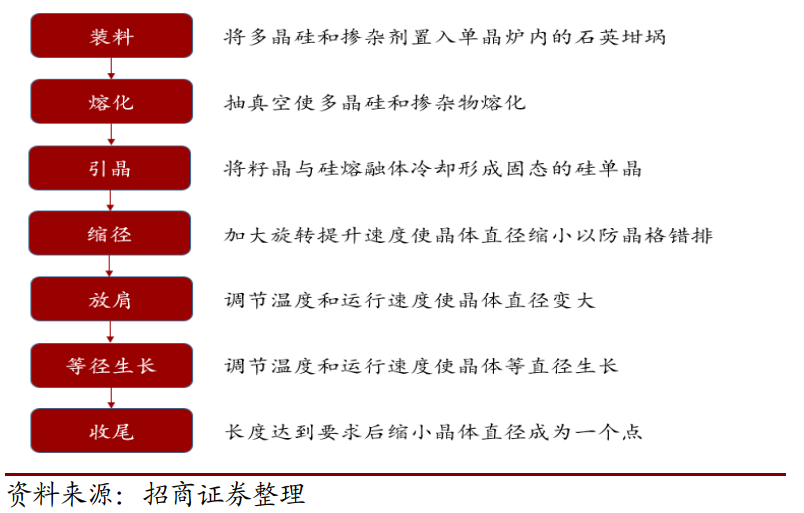

首先第一阶段硅片制备,开采半导体材料并根据半导体标准进行提纯。硅片以沙子为原料,通过转化可以成为具有多晶硅结构的纯净硅,形成带有特殊电子和结构参数的晶体,之后在晶体生长和晶体准备工艺中,晶体被切割成称为晶圆的薄片,并进行表面处理。

第二阶段晶圆制造,就是在表面形成器件或集成电路。 在每个晶圆上通常可形成200-300 个同样的器件,也可多至几千个,晶圆制造有几千个步骤,可以分为两大主要部分:前段工艺线( FEOL)是晶体管和其他器件在晶圆表面形成的,后端工艺线( BEOL)是以金属线把器件连在一起并加一层最终保护层。

第三阶段晶圆封测,在第二阶段晶圆制造后,晶圆上的芯片已经完成,但是仍旧保持晶圆形式并未经测试,因此每个芯片都需要晶圆电测来检测是否符合客户要求。 随后进行封装,是指通过一系列过程把晶圆上的芯片分隔开,然后将它们封装起来,保护芯片免受污染和外来伤害的作用,并提供坚固耐用的电气引脚以和电路板或电子产品相连,这个阶段最后还有芯片最终测试,因此称为晶圆封测。

图3:成熟市场 IC 制造设备投资占比情况

1、硅片制备

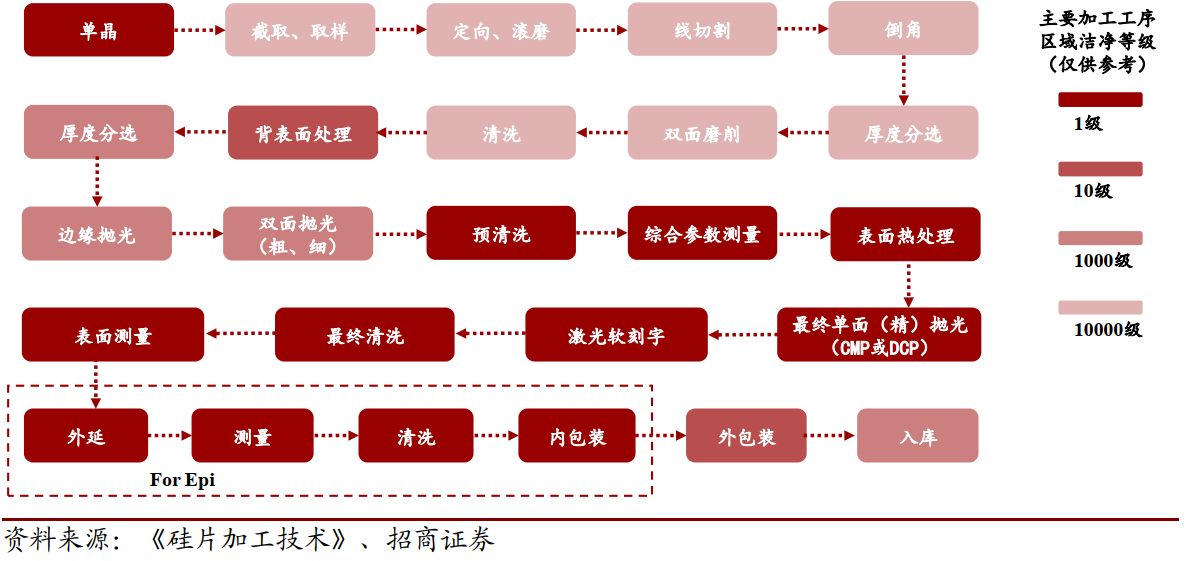

硅片质量要求越来越高,加工流程也水涨船高,越来越精细。目前集成电路技术早已经迈进线宽工艺小于 0.1 微米的纳米电子时代,对硅单晶抛光片的表面加工质量要求愈来愈高,为保证硅抛光片的翘曲度、表面局部平整度、表面粗糙度等具有更高的加工精度,尤其是对大直径硅抛光片进行更加细致的加工,目前硅片制备主要步骤可以概括为:拉晶-切片-磨片-倒角-刻蚀-抛光-清洗-晶圆测试。

图4:直径 300mm 硅抛光片典型的加工工艺流程

1.1、拉晶—单晶炉 41 亿市场

晶体生长:半导体晶圆是从大块硅锭切割后的结果,而硅锭是从大块具有多晶结构和未掺杂本征材料生长得来。把多晶块转变成一个大单晶,给予正确的定向和适量的 N 型或 P 型掺杂,这就是晶体生长,而晶体生长主要通过三种方法:直拉法、液体掩盖直拉法和区熔法。采用直拉法(包括液体掩盖直拉法)的硅单晶约占 85%,其他则采用区熔法,直拉法生长的硅单晶主要用于生产低功率的集成电路和分立元件(如 DRAM、SRAM、ASIC 电路和各种晶体管),更容易获得高含氧量和大直径的硅锭,而区熔法生产的硅单晶,成本较高,具有电阻率均匀、氧含量低、金属污染低等特性,故主要生产高反压、大功率的电子元件(如电力整流器、晶闸管、功率集成电路等)。

无论是直拉法还是区熔法,使用的设备均为单晶炉,单晶炉由炉体、热场、磁场、控制装置等部件组成,其中控制炉内温度的热场和控制晶体生长形状的磁场是决定单晶炉生产能力的关键。 单晶炉主要是以进口设备为主,如德国 CGS 公司和美国 KAYEX 的直拉单晶炉都是口碑较好的老牌产品,此外还有德国 PVA、日本 FERROTEC 等,但目前国内已经实现部分单晶炉国产化,8 英寸单晶炉逐步开始国产化,12 寸单晶炉尚无批量供货,国内的晶盛机电、南京京能、西安理工晶科等是单晶炉先行者。其中晶盛机电承担的 02 专项“300mm 硅单晶直拉生长设备的开发”、“8 英寸区熔硅单晶炉国产设备研制”两大项目,均已通过专家组验收。 晶盛的 8 寸直拉单晶炉和区熔单晶炉均已实现了产业化,为中环半导体、 有研半导体、环欧半导体、金瑞泓等国内知名半导体硅片生产商累计供应了几十台设备。单晶炉投资占硅片制备设备的投资 25%左右,预计到2020 年新增需求为 40.5 亿元,是逐渐加快进口替代的设备行业。

图5:拉晶工序图

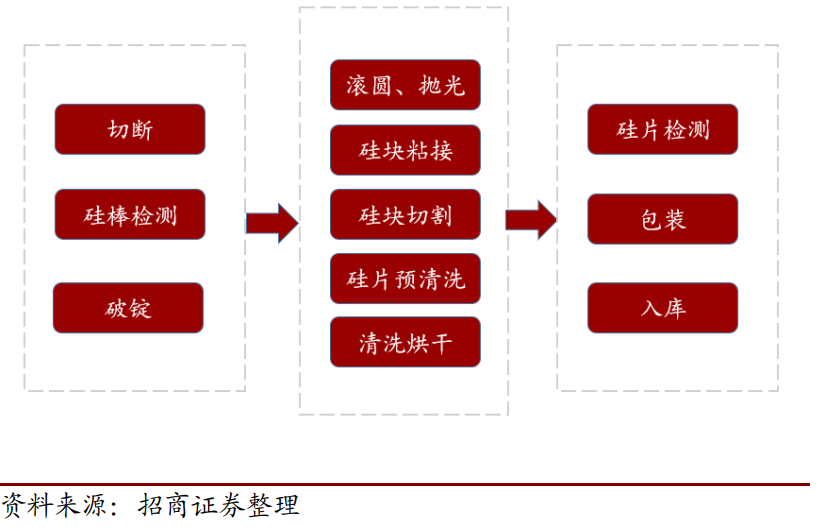

1.2、切片: 8 亿市场

晶体生长之后变进入晶圆准备环节,第一步是硅切片加工。 硅切片加工的目的在于将硅锭切成一定厚度的薄晶片,切后的参数如晶向偏离度、 TTV 等精度对后道工序的加工(如研磨、刻蚀和抛光等)起直接作用,主要包括切去两端、硅片定位、精准切割等步骤,切割通常有外圆、内圆和线切割三种方式,小直径硅锭多采用内圆切片机加工,而线切割工艺则具有更高的加工精度和更小的切口材料损耗,目前大于 200mm 的硅锭均采用线切割系统。以加工直径 200mm 硅单晶为例,切片厚度为 800 微米,每千克单晶出片约为 13.4 片,切割成本每片约 1.51 美元,线切割机的产量是内圆切割机的 5 倍以上、线切割机的切割运行成本可低于內圆切割机运行成本 20%以上。

切片工序主要应用的设备包括切割机、 滚圆机、截断机等。 由于精度要求高,国内和国外技术差别较大,因而目前以进口设备为主,主要有日本的东京精密、齐藤精机、瑞士HCT、 M&B 等,国内的晶盛机电在 2018 年展成功推出 6-12 英寸半导体级的单晶硅滚圆机、单晶硅截断机,中电科 45 所能提供部分切片机产品。切片设备占硅片制备设备的投资 5%左右,预计到 2020 年我国新增需求为 8.1 亿,也是继续进口替代的行业。

图6:切片工序图

1.3、磨片: 几乎完全进口

半导体晶圆的表面要光滑规则,并且没有切割损伤,完全平整,因此需要磨片处理。 要求来自于很小尺寸制造器件的表面和次表层面,平整度是小尺寸图案绝对必要条件,先进的光刻工艺把所需的图案投影到晶圆表面,如果表面不平,投影将会扭曲。而平整则需要磨片,是一个传统的磨料研磨工艺,精调到半导体使用的要求。主要包括双面磨削(直径小于 300mm)和表面磨削(直径大于 300mm),双面磨削加工损耗较大,而表面磨削损耗较小。磨片步骤使用的设备为研磨系统,和切片设备一样,几乎完全是进口。 国外品牌包括日本 KoYo、 NTC、 Okamoto 和德国 Peter Wolters 等,国内无相应产品,占硅片设备投资 5%左右,到 2020 年新增需求 8.1 亿。

图7:磨片工序图

1.4、倒角设备

倒角是要消除硅片边缘表面由于经切割加工后产生的棱角、毛刺、崩边、裂缝或其他缺陷和各种边缘表面污染,从而降低硅片边缘表面的粗糙度,增加硅片边缘表面的机械强度,减少颗粒的表面玷污。主要使用的设备是倒角机,一般分为 T 形磨轮和 R 形磨轮,R 形磨轮比 T 形磨轮加工效率高 30%作用,倒角机系统仍然是国外垄断,日本 TSK、日立,德国博世等技术领先,占硅片制备设备投资 5%左右,预计到 2020 年我国新增市场空间为 8.1 亿。

图8:倒角工序图

1.5、刻蚀机(硅片制备环境) 16 亿市场

硅刻蚀是一种化学腐蚀工艺,包括酸腐蚀和碱腐蚀。 硅晶片在经过切片、研磨等机械加工后,表面因机械加工应力而形成有一定深度的机械应力损伤层,而且硅片表面有金属离子等杂质污染,通常采用化学腐蚀工艺(酸腐蚀或碱腐蚀)来消除这些影响,化学腐蚀的厚度去除总量一般是 30-50 微米,酸腐蚀后硅晶片各个结晶方向会受到均匀的化学腐蚀,速度较快,硅片表面比较光亮,不易吸附杂质,但平坦度差、较难控制,而碱腐蚀虽然速度慢,但硅片表面比较平坦,但又比较粗糙易吸附杂质。刻蚀流程所采用的设备为刻蚀设备。国外产品包括美国 SEMITOOL、德国 RENA 等,国内逐渐开始进口替代,主要以北方华创(等离子硅刻蚀机)和中微半导体(等离子介质刻蚀机)为主,刻蚀设备占硅片设备投资 10%左右,未来两年共 16.3 亿市场。

图9:刻蚀工序图

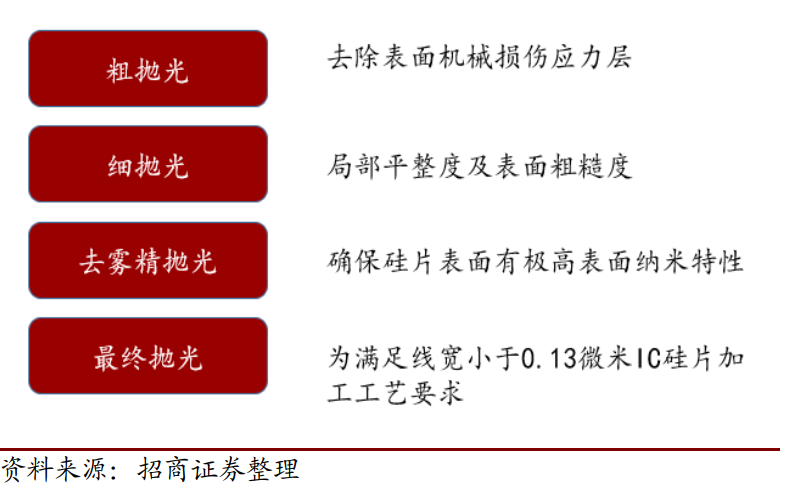

1.6、抛光: CMP 设备 40 亿市场

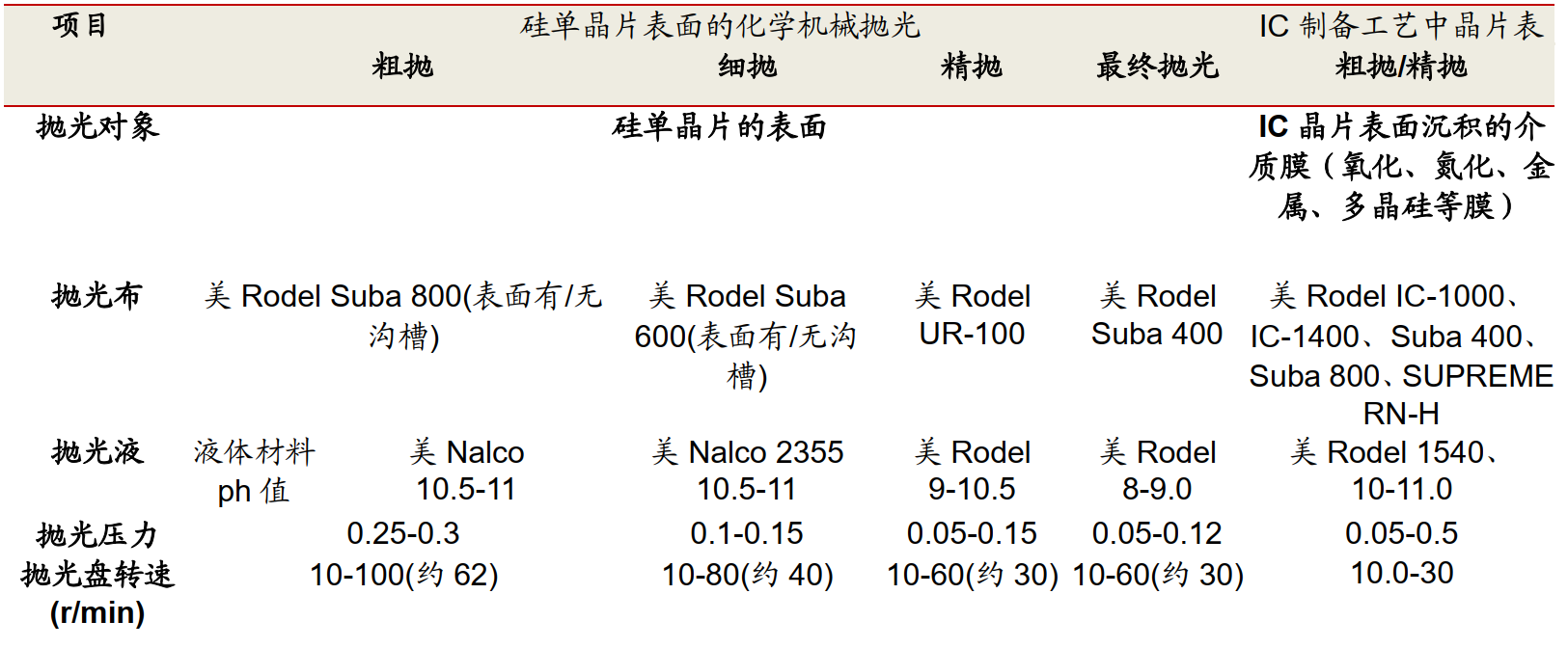

抛光目的在于去除前序切片、研磨等残留的微缺陷及表面应力损伤层和去除表面的各种金属离子等杂志污染,以求获得硅片表面局部平整、表面粗糙度极低的洁净、光亮“镜面”,满足制备各种微电子器件对硅片的技术要求。流程包括粗抛、细抛、精抛和最终抛光,值得注意的是,硅片表面的化学机械抛光 CMP 技术和 IC 制备工艺中的晶片表面平坦化 CMP 是两种不同的抛光工艺,两者在抛光对象、抛光布、抛光液、抛光压力、转速等方面均有较大差别。

目前国内仍以国外为主,但已经开始了国产化进程。 国内晶盛机电率先取得突破, 2018年成功研发出 6-8 英寸的全自动硅片抛光机,未来有望将产品拓展至 12 英寸抛光设备。国外以美国 Revasum、日本 Speed Bfam、 KOVAX,荷兰 ASML 等为主,占硅片制备设备投资约 25%,预计到 2020 年共 40.5 亿市场。

图10:抛光工序图

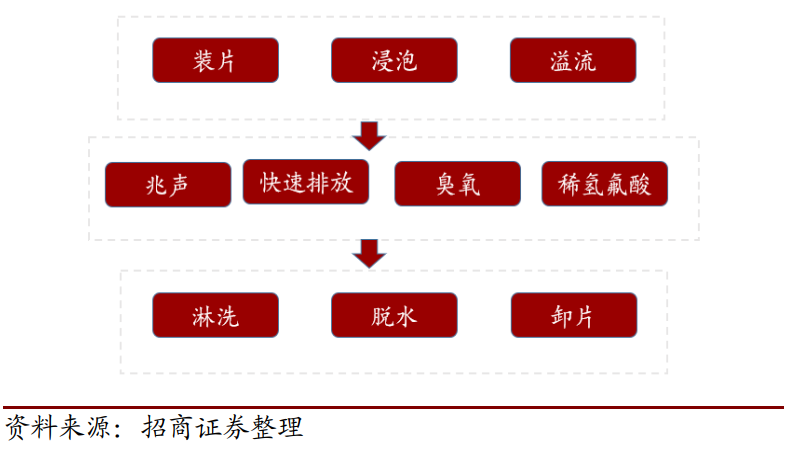

1.7、清洗设备-约占硅片设备 10%

硅片经过不同工序加工后,表面已经收到严重污染,硅片清洁的目的在于清除表面的微粒、金属离子及有机物沾污等。一般先通过强氧化剂使“电镀”附着到硅表面的金属离子氧化成金属,溶解在清洗液或者附在硅片上,然后用小直径正离子替代吸附在硅片表面的金属离子,使之溶解在清洗液中,最后用大量去离子水进行超声波清洗,以排除溶液中的金属离子。

清洗设备目前国内已经开始进口替代,但高端市场仍被国外垄断。北方华创、盛美半导体、至纯科技为国内清洗设备“三剑客”,其中盛美半导体是国内唯一跨入 14nm 产线验证的清洗设备厂商,技术上已经具备国际竞争力。但高端市场仍被全球半导体晶圆清洗设备市场的前三名厂商 LamResearch、东京电子和 DNS 垄断,在 2015 年占据市场87.7%的份额。清洗设备占硅片制备设备投资约 10%,预计到 2020 年共 16.2 亿市场。

图11:清洗工序图

1.8、晶圆检测:检测设备 24 亿市场

晶圆检测主要是对表面缺陷检测。硅单晶、抛光片的电学、物理和化学等性质以及加工精度将直接影响集成电路制备的特性和成品率,为了满足对硅单晶、抛光片的高要求,必须采用先进的测试方法,对硅单晶的晶向、缺陷、氧含量、碳含量、电阻率、导电型号、少数载流子浓度、等技术参数有效测试,对抛光片表面缺陷(点缺陷、错位、层错等),颗粒污染和沾污进行检测。

检测设备包括厚度仪、颗粒检测仪、硅片分选仪等。目前国产设备涉足较少,主要以进口设备为主,包括日本 Advantest、美国 MTI 等公司,检测设备占硅片制备设备投资约15%,预期未来两年共 24.3 亿市场。

1.9、硅片供不应求,设备国产化正当时

供给端—全球硅片出货量维持高位。硅片是半导体芯片制备的基础原材料,目前 90%以上的芯片和传感器是基于半导体单晶硅片制造而成,2018 年我国硅片占晶圆厂制造材料的总比重高达 30%,是不可或缺的制备材料,2018 年全球硅片出货接近 130 亿平方英寸,增速 7.81%。需求端—硅片需求继续攀升。在经历了 2018 年硅片需求的高速增长后,尽管 2019 年下游景气度不佳,但 IHS Markit 估计 2019 年硅片需求仍将继续增长 3.6%,供应缺口会一直延续到 2022 年。

供需缺口将成常态,国产硅片势在必行。 供不应求和寡头垄断的格局下( 五大半导体硅片供应商市场规模合计占 94%),硅片价格水涨船高, 2016-2018 年间硅片价格暴涨40%。面对这一情况,我国只能大幅兴建晶圆制造厂,根据 SEMI 统计,过去两年间,全球新建 17 座 12 寸晶圆制造厂,其中有 10 座位于中国大陆;从 2017 年到 2020 年,预计全球新增半导体产线 62 条,其中 26 条位于中国大陆。 晶圆制造厂的大量兴建,必然催生硅片制备设备的需求,由此为设备国产化带来突破契机。

产能供不应求,硅片设备刚需 162 亿,硅片制造工序为拉晶—切片—磨片—倒角—刻蚀—抛光—清洗—检测,其中拉晶、抛光和检测为硅片制造核心环节,对应设备分别为单晶炉(占整体设备价值量 25%)、 CMP抛光机( 25%)、检测设备( 15%)。 目前,硅片制造设备主要被日韩、欧美企业垄断,代表厂商有德国 CGS、日本齐藤精机、 KoYo 等。国产设备由于起步较晚,在硅片制造环仍处于发展阶段,进口替代市场极大,代表厂商有晶盛机电、北方华创、中微半导体等,其中晶盛机电的 8 英寸单晶炉逐步开始实现国产化替代, 12 寸单晶炉开始小批量生产,现已交付上海新昇使用,并在 SEMICON China 2018 展会上推出了滚圆机、截断机、双面研磨机、全自动硅片抛光机等新品设备,进一步向硅片制造全制程延伸。

图12:硅片制备设备全景图

国内需求缺口大,硅片制备迎来“野蛮生长期”,设备投资迎来高峰。 根据芯思想研究院的统计数据, 2018-2020 年,我国对 8 英寸硅片的需求量将从 90 万片/月上升至 180万片/月,新增需求 80 万片/月。12 英寸硅片的需求量从 60 万片/月上升到 105 万片/月,新增需求量 45 万片/月。假设 8 英寸和 12 英寸每 10 万片投资额分别为 6 亿元和24 亿元,潜在新增设备需求为 54 亿元和 108 亿元, 目前我国 4-6 英寸硅片已经完全资产,因此主要设备需求都在 8 英寸和 12 英寸,因此预计 2018-2020 年硅片设备国内新增设备投资额为 162 亿元。

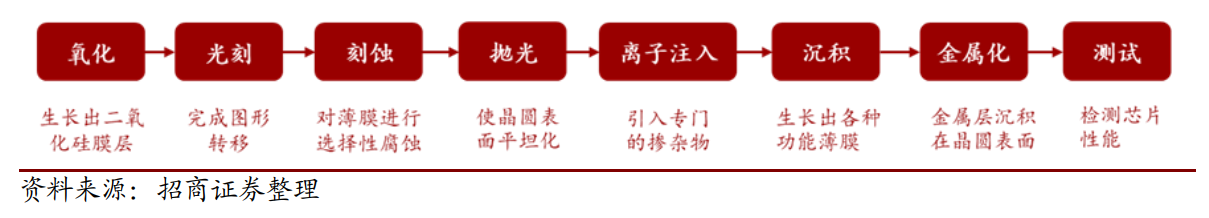

2、晶圆制造

晶圆制造是最复杂且资金投入最多的环节,是千亿大市场,核心设备国产化刻不容缓。自硅片开始的晶圆制造是第二阶段,硅片经过氧化、沉积、蚀刻及离子注入等步骤反复处理,成为一整套集成电路。 晶圆制造就是裸露的硅片到达工厂,然后经过各种清洗、成膜、光刻、刻蚀和掺杂处理,成为永久刻蚀在硅片上的一整套集成电路。具体来说,就是在硅晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),这个步骤为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万美元一台,其所需制造环境为温度、湿度与含尘量均需控制的无尘室,虽然详细的处理程序是随著产品种类与所使用的技术有关,不过其基本处理步骤通常是晶圆先经过适当的清洗之后,接著进行氧化及沉积,最后进行显影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。

图13:晶圆制造工序

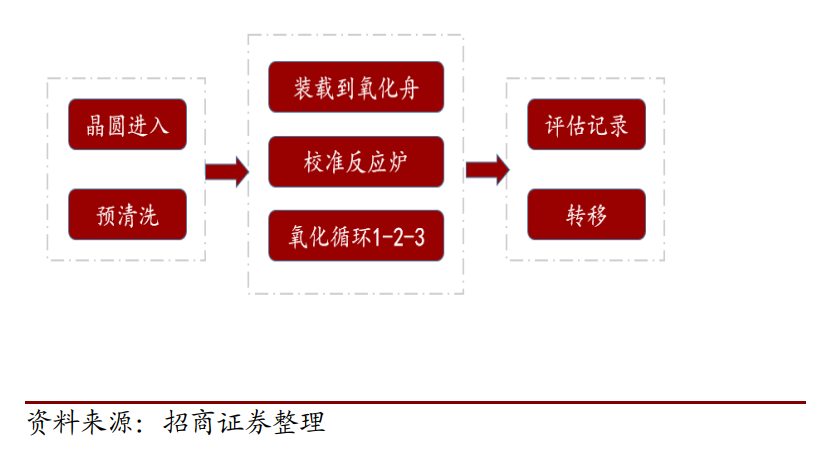

2.1、氧化: 氧化炉 20 亿美元市场

氧化目的在于生成二氧化硅薄膜。用硅作为原材料的一个重要原因就是硅容易生长出二氧化硅膜层,这样在半导体上结合一层绝缘材料,再加上二氧化硅的其他特性,使得二氧化硅成为硅器件制造中得到最广泛应用的薄膜。可以用来处理硅表面,做掺杂阻挡层、表面绝缘层,以及器件中的绝缘部分。半导体二氧化硅是高浓度的,经过特定方法制成,即是在氧化剂及逐渐升温的条件下,光洁的硅表面生成的,这种工艺称为热氧化。二氧化硅层在常压或高压条件下才能生长,常压氧化发生在不必有意控制内部压力的系统中(也就是大气压),目前有两种常压技术:管式反应炉和快速氧化系统,也因此有两种氧化炉:传统管式反应炉和快速热处理设备( RTP)。 RTP 相对于传统管式反应炉的区别在于, RTP 甚至可以以每秒 50-100 摄氏度的速率达到 800-1050 摄氏度的工艺温度,而传统反应炉需要几分钟才可以,相应的也可以迅速冷却。此外随着晶圆直径越来越大,对均匀度的要求也更倾向于采用单片工艺的 RTP。

图14:氧化工序图

传统管式反应炉约占晶圆制造设备投资 5%, RTP 设备约占 2%。预计 2019/2020年氧化炉的市场空间为 8.8 亿美元、 11.93 亿美元, RTP 设备市场空间 2.51 亿美元、3.41 亿美元,并且已经开始进口替代。国外主要厂家有英国 Themco 公司、Centrotherm thermal Solutions 公司等,国内北方华创的氧化炉目前已经批量应用于中芯国际、华力微电子、长江存储等厂商,此外中电科 48 所、青岛旭光等也取得重大进展。

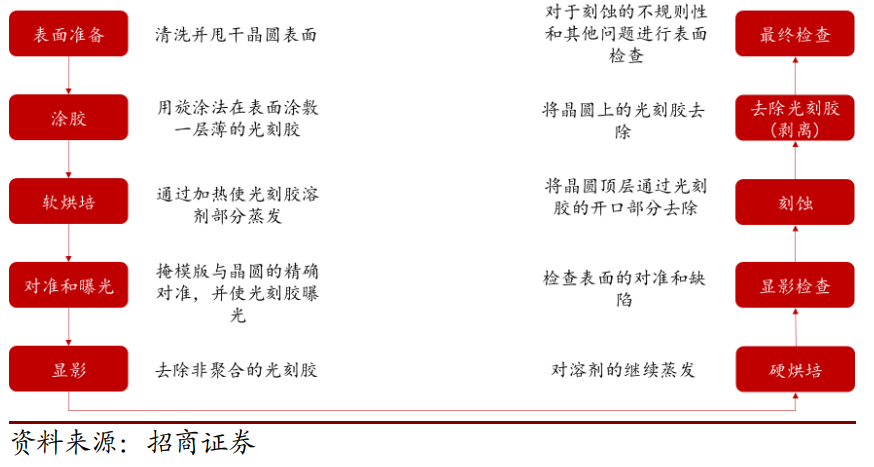

2.2、光刻:光刻机 90 亿美元市场

从光刻开始就进入图形化工艺阶段,图形化工艺是在晶圆内和表面层建立图形的一系列加工,这些图形根据集成电路中物理器件的要求来确定其尺寸和位置,是半导体工艺过程中最重要的工序之一。 光刻工艺主要有两个目标,一是在晶圆中和表面产生图形,这些图形的尺寸在集成电路或者器件设计阶段建立,二是将电路图形相对于晶圆的晶向及以所有层的部分对准的方式,正确地定位于晶圆上。一种集成电路工艺要求 40 个以上独立的光刻(或掩模)步骤,图形定位的要求就好像是一栋建筑物每一层之间所要求的而正确对准,如果每层无法和上一层精确对准将导致整个电路的失效,因此光刻对精度要求非常高,是技术壁垒最高的工艺之一。

光刻工艺和照相、蜡纸印刷比较接近的一种多步骤的图形转移过程。开始将一个电路的设计转化为器件和电路的各个部分的 3 个维度,接下来绘出 X-Y(表面)尺寸、形状和表面对准的复合图。然后将复合图分割成单独掩模层(一套掩模)。这个电子信息被夹在到图形发生器中,来自图形发生器的信息又被用来制造放大掩膜版和光刻掩模版,或者信息可以驱动曝光和对准设备来直接将图形转移到晶圆上。

概括而言,图形转移是通过两步完成的。 第一次图形被转移到光刻胶层,光刻胶类似胶卷上所涂的感光物质,曝光后会导致自身性质和结构的变化,比如负胶会产生聚合现象,即光刻胶被曝光的部分由可溶性物质变成了非溶性物质,反之则成为正胶。第二次图形转移是从光刻胶层到晶圆层,当刻蚀剂把晶圆表面没有被光刻胶盖住的部分去掉时,图形转移就发生了。

具体的转移过程称为光刻十步法,第 1 步到第 7 步之间发生了第一次图形转移,第 8-第 10 步中图形被转移到了晶圆表面层(第二次图形转移)。

图15:光刻“十步”工序图

光刻工艺需要的设备就是光刻机,光刻机根据原理不同可分为三代: 第一代(接触式光刻机、接近式光刻机)、第二代(扫描投影光刻机)、第三代(步进式光刻机、步进扫描式光刻机)。第一代接触式光刻机属于 20 世纪 70 年代应用最广的光刻机,主要用于分立器件产品、小规模( SSI)和中规模( MSI)集成电路,以及大约在 5 微米或者大的特征图形尺寸,还可以用于平板显示、红外传感器、器件封装和多芯片封装( MCM),但是之所以被取代,主要是由于掩模版与晶圆的接触带来的良品率损失。接近式光刻机属于接触式光刻机的加强版,而扫描投影光刻机则属于第二代,它采用了带有夹缝的反射镜系统,夹缝挡住了部分来自光源的光,也就是用扫描技术避免全局掩模曝光投影产生的问题。第三代步进式光刻机原理则是把图像从掩模版分步曝光到晶圆表面上,带有一个或几个芯片图形的放大掩模版被对准、曝光、然后步进到下一个曝光场,重复这样的过程,这样放大掩模版比全局掩模版的质量高,因此产生缺陷的数量就更小,而且每次曝光区域变小,分辨率也得以提高。步进光刻机的难度在于自动对准系统。

目前世界上最大的光刻机制造商是荷兰 ASML。 1984 年 ASML 从飞利浦独立出来,专门致力于研发光刻技术,得益于近乎完美的德国机械工艺以及世界顶级光学厂商德国蔡司镜头, 再加上美国提供的光源, ASML 迅速发展,到如今占到了全球光刻机总销售收入的 80%,其他如尼康则在中低端光刻机领域耕耘,在极紫外光(EUV)领域,目前 ASML处于完全垄断地位。曾经一台高端设备卖到了 1 亿欧元。荷兰是全球为数不多拥有完整半导体产业链的国家,其半导体产业年收益高达百亿欧元以上,全球超过四分之一的半导体设备来自荷兰。

光刻机这种高精度光机一体化设备,研发过程没有什么捷径可走,精度只能一步步提升。没有一微米的基础,就不可能造 90 纳米的设备,没有 90 纳米的基础,就不可能造 45纳米的设备。现在 ASML 可以造 10 纳米以内精度的设备,也是一步步积累出来的。除了荷兰 ASML 外,德国 SUSS、日本尼康、美国 Ultratech 等也具有较强实力。 这些年来,国内早就有设备厂商,以及研究机构在对光刻机进行研发。如上海微电子、中电科四十五所、中电科四十八所等。上海微电子,则研发出了中端的投影式光刻机。 2016年初,光刻机核心子系统双工件台系统样机研发项目通过内部验收,为我国自主研发65nm 至 28nm 双工件干台式及浸没式光刻机奠定了基础。光刻机约占晶圆制造设备投资 30%,预计 2019/2020 年我国光刻机市场空间为 37.68 亿美元、 51.12 亿美元。

2.3、刻蚀:刻蚀机 35 亿美元市场

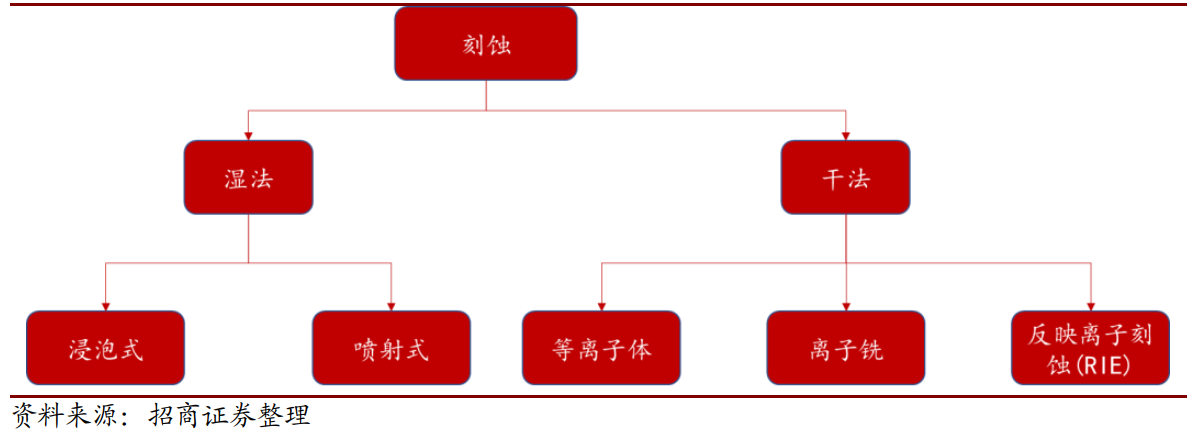

晶圆完成对准和曝光后,器件或电路的图案将以曝光和未曝光区域的形式记录在光刻胶上通过对为聚合光刻胶的化学分解来使图案显影。完成显影后,掩模板就被固定在光刻胶膜上并准备刻蚀,在刻蚀后图形就会被永久的转移到晶圆的表层,刻蚀就是通过光刻胶暴露区域来去掉晶圆最表层的工艺,主要分为两大类:湿法刻蚀和干法刻蚀。

湿法刻蚀是使用液体刻蚀沉浸的技术,晶圆沉浸于装有刻蚀剂的槽中,经过一定的时间,传递到冲洗设备去除残留的酸,再送到最终清洗台以冲洗和甩干。相对于干法刻蚀,湿法刻蚀有众多缺陷,比如局限于 2 微米以上的图形尺寸、容易导致边侧形成斜坡、要求冲洗和干燥步骤等,因此干法刻蚀被用于先进电路的小特征尺寸精细刻蚀中,并且在刻蚀率、辐射损伤、微粒产生等方面拥有较大优势,包括等离子体刻蚀、离子铣刻蚀及反应离子刻蚀。刻蚀后再通过剥离技术去除光阻层。

图16:刻蚀工艺简介

刻蚀机约占晶圆制造设备投资 12%,预计 2019/2020 年我国刻蚀机空间为 15.07 亿美元、 20.45亿美元,行业已经开始进口替代,海外主要是美国应用材料公司、美国泛林等。国内主要是北方华创在硅刻蚀机领域实现了14nm的突破,同时也在去年实现了适用于 8 英寸晶圆的金属刻蚀机的研发和生产,即将登录科创板的中微半导体的介质刻蚀机自主研发的 5nm 等离子体刻蚀机经台积电验证,性能优良,将用于全球首条 5nm制程生产线。

2.4、抛光: CMP 抛光机 9 亿美元市场

化学机械抛光( CMP)兼具有研磨性物质的机械式研磨与酸碱溶液的化学式研磨两种作用,可以使晶圆表面达到全面性的平坦化,以利后续薄膜沉积之进行。在 CMP 制程的硬设备中,研磨头被用来将晶圆压在研磨垫上并带动晶圆旋转,至于研磨垫则以相反的方向旋转。在进行研磨时,由研磨颗粒所构成的研浆会被置于晶圆与研磨垫间。影响CMP 制程的变量包括有:研磨头所施的压力与晶圆的平坦度、晶圆与研磨垫的旋转速度、研浆与研磨颗粒的化学成份、温度、以及研磨垫的材质与磨损性等,因此对 CMP抛光机质量要求很高。

预计 2019/2020 年抛光机空间 3.77 亿美元、 5.11 亿美元。参与企业有美国应用材料公司、Rtec 公司等,国内有中电科装备、盛美半导体等。中电科装备的8寸 CMP 设备已经进入中芯国际生产线进行工艺验证,12 英寸的设备也在研发当中。

图17:硅单晶表面和 IC 设备表面 CMP 抛光不同

2.5、掺杂和 CVD 沉积:CVD设备 60 亿美元市场

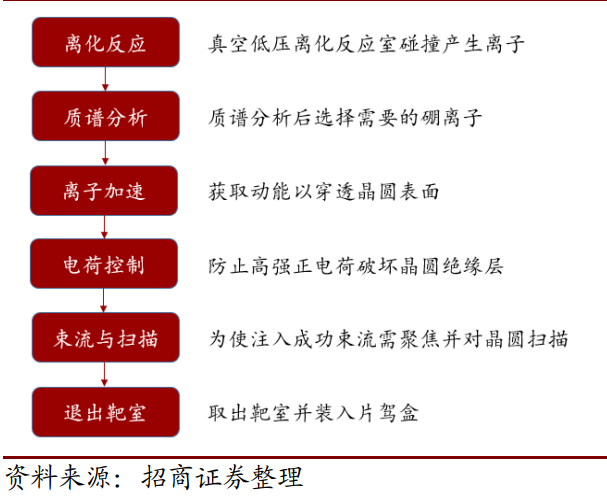

掺杂目的在于形成 PN 结。 半导体材料的特性之一就是导电性和导电类型( N 型和 P 型)能够通过在材料中掺入专门的杂质而被产生和控制,通过引入专门的掺杂物,形成使晶体管和二极管工作的 PN 结。主要有两种方式:采用离子注入或热扩散工艺,在晶圆表面形成结。热扩散是指通过加热,将掺杂材料散布到晶圆体内,而现在离子注入已经逐渐取代了较老的热扩散工艺,并且在当今的小型和多种结构器件方面起作用,与热扩散不同,离子注入是物理过程,也就是说注入动作不依赖于杂质与晶圆材料的化学反应,意味着工艺在接近室温下可以进行,宽范围浓度的掺杂成为可能,并可以对晶圆内掺杂的位置和数量进行更好的控制,因此广泛应用于先进电路的掺杂步骤。

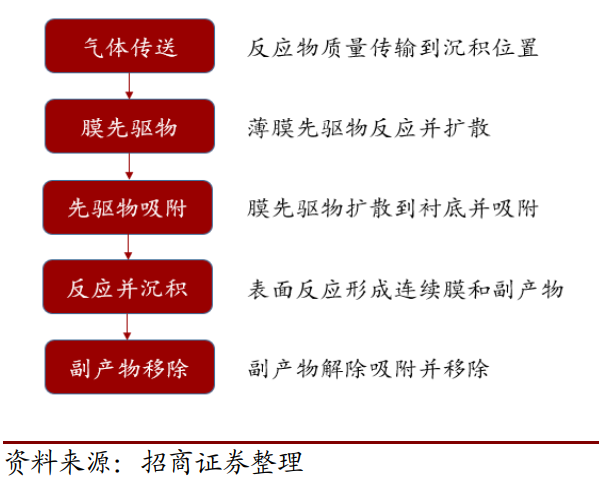

虽然掺杂的区域和 PN 结的形成电路中的电子有源原件的核心,但是需要各种其他半导体、绝缘介质和导电层完成器件,并促使这些器件集成为电路,化学气象淀积( CVD)就是将这些层加到晶圆表面。 CVD 沉积之后产生的薄层具有各种作用,包括外延层、绝缘介质层、金属导体层、最终的钝化层等。并且播磨需要具有均匀的厚度以同时满足电性能和机械性能的要求,也必须具有平整光滑的表面,以及必须无应力且不含有不需要的化学元素,是较为复杂的工艺

CVD 沉淀的工序中,氧化是以循环的方式进行的,首先将晶圆装载到反应室内,装载过程通常是在惰性气体环境下进行的,然后晶圆被加热到预定温度,将反应气体引入淀积薄膜的反应室内进行反应,最后将参与反应的化学气体排出反应室,移出晶圆。

图18:离子注入机工序

图19:CVD 膜生长过程

预计 2019/2020 年离子注入机的市场空间为 5.02 亿美元、6.82 亿美元。 国外厂商有美国 AMAT 公司等,目前国内能生产离子注入机的企业只有中电科电子装备公司,其 12英寸中束流离子注入机以优秀等级通过国家 02 专项实施管理办公室组织的验收, 2015年在中芯国际完成了 55nm、 45nm 和 40nm 的小批量产品工艺验证,到 2017 年中束流离子注入机已经在中芯国际实现了稳定流片 200 万片。目前中电科的大束流离子注入机已经进驻中芯国际。

2.6、PVD 沉积: PVD 沉积设备 35 亿美元市场

PVD 沉积主要是一种物理制程而非化学制程。 此技术一般使用氩等惰性气体,藉由在高真空中将氩离子加速以撞击溅镀靶材后,可将靶材原子一个个溅击出来,并使被溅击出来的材质(通常为铝、钛或其合金)沉积在晶圆表面。 PVD 以真空、测射、离子化或离子束等方法使纯金属挥发,与碳化氢、氮气等气体作用,加热至 400~ 600℃(约1~ 3 小时)后,蒸镀碳化物、氮化物、氧化物及硼化物等 1-10 微米厚之微细粒状薄膜。

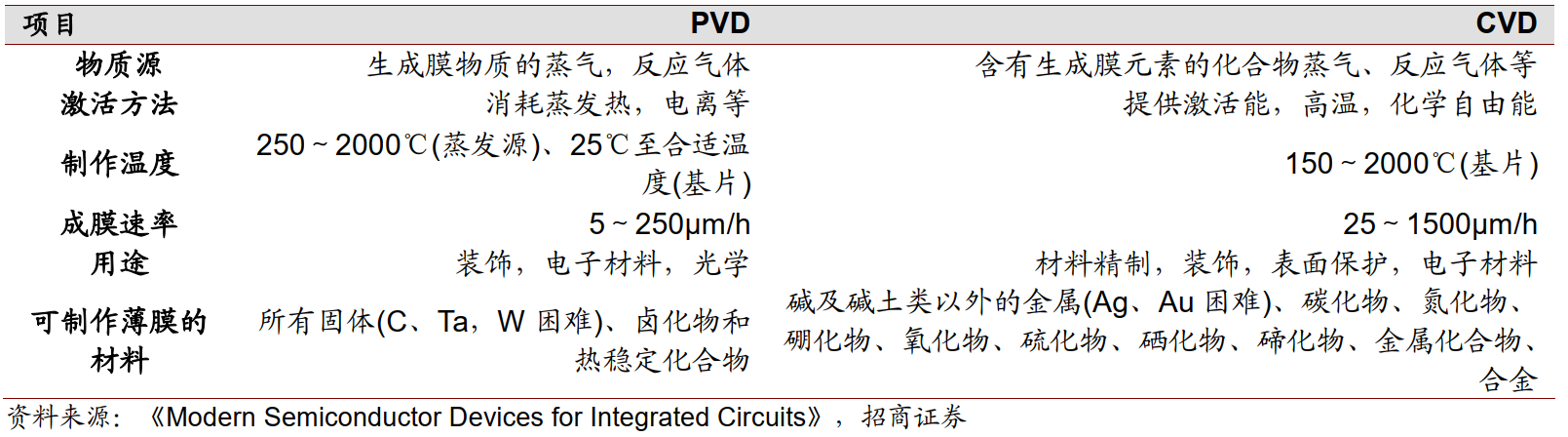

对比 CVD 和 PVD 薄膜的沉积方法,两者根据其用途的不同而不同,形成薄膜的厚度通常小于 1um,有绝缘膜、半导体薄膜、金属薄膜等各种各样的薄膜。 CVD 法有外延生长法、 HCVD, PECVD 等。 PVD 有溅射法和真空蒸发法。一般而言, PVD 温度低,没有毒气问题; CVD 温度高,需达到 1000 摄氏度以上将气体解离,来产生化学作用。PVD 沉积到材料表面的附着力较 CVD 差一些, PVD 适用于在光电产业,而半导体制程中的金属导电膜大多使用 PVD 来沉积,而其他绝缘膜则大多数采用要求较严谨 CVD技术。 PVD 形成的硬质薄膜具有高强度,耐腐蚀等特点。

预测 2019/2020 年 PVD 设备空间为 15.07 亿美元、 20.45 亿美元, CVD 设备空间为25.12 亿美元、 34.08 亿美元。 薄膜沉积设备主要的生产企业包括美国应用材料公司、美国 PVD 公司、美国 Vaportech 公司、泛林半导体、荷兰 ASM 公司、日本 Tokki 公司等,而国内企业包括北方华创、沈阳拓荆等,北方华创是国内薄膜沉积领域的领先者,目前技术达到 14nm,未来会向 12nm 等更小节点推进工艺。

图20:PVD 工序

图21:PVD 和 CVD 方法的比较

2.7、晶圆中测:国内尚处起步阶段

在晶圆完成制造之前,会有一步晶圆中测,相当于晶圆生产过程中的报告卡,属于后道工序环节( ATE)。 在测试过程中,会检测每一个芯片的电性能和电路功能,因此又称为芯片分选或电分选。在测试时,晶圆被固定在真空吸力的卡盘上,并将很细的探针对准芯片的每一个压点使其接触,从而检测是否合格,重复对每一个电路进行电测试。目的是在送往封装工厂前,鉴别出合格的芯片。

晶圆中测检测设备包括 CDSEM(扫描电镜)、 AOI(自动光学检测机)等,美国的KLA-Tencor、美国应用材料、日本 Hitachi、美国 Rudolph 公司、以色列 Camtek 公司等,国内主要有上市公司长川科技,上海睿励科学仪器等,但目前与国际巨头还有一定差距。

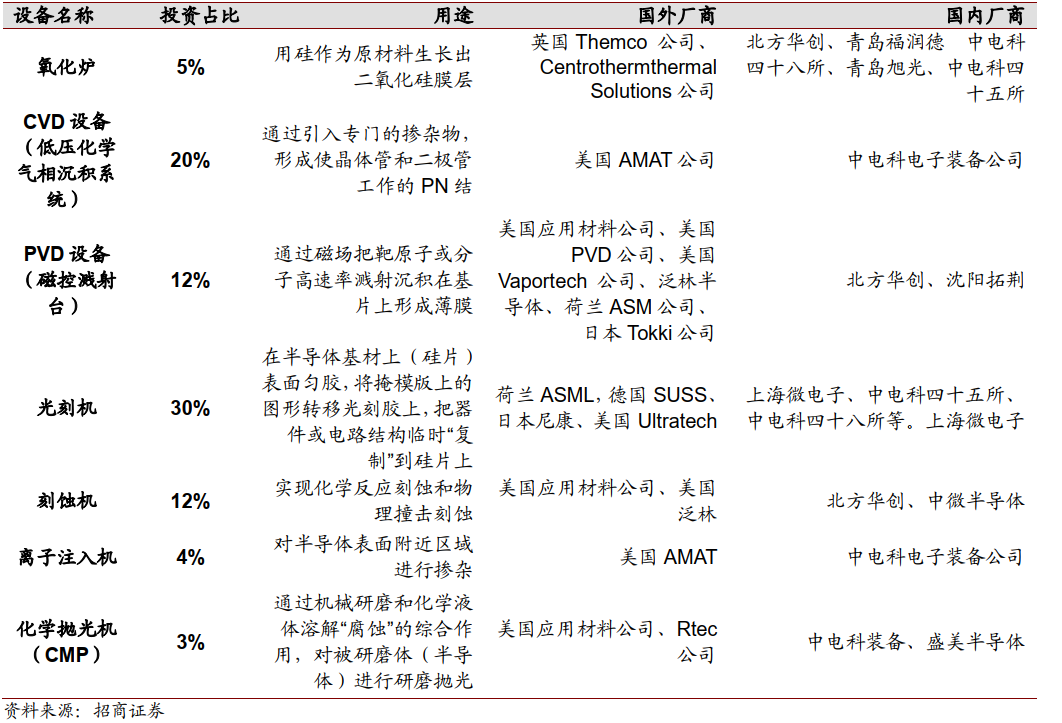

2.8、光刻机、刻蚀机、薄膜沉积设备在整个晶圆制造中占比最大

晶圆制造环节是生产链条里最重资产的一环,成熟市场的设备投入占总设备比在70%-80%之间。 晶圆制造工序分别是氧化—光刻—刻蚀—抛光—掺杂和 CVD 沉积/PVD沉积—晶圆中测,主要涉及到的生产设备分别是氧化炉、光刻机、刻蚀机、 CMP 抛光机、离子注入机、薄膜沉积设备、清洗机和检测机,其中光刻机、刻蚀机和薄膜沉积设备的价值量最大,生产难度也最高。

美国、欧洲、日本等国家在晶圆制造设备上远远领先其他国家,我国尽管开始突破,但仍处于起步阶段。 北方华创在氧化炉、 PVD 沉积设备、刻蚀机等领域取得重大突破,甚至部分产品已经批量供货,中电科也取得一定突破。根据 SEMI 预计, 2019/2020 年我国半导体设备市场空间为 126 亿美元、 170 亿美元。

图22:晶圆制造设备投资占比情况及国内、国外参与公司

3、晶圆封测

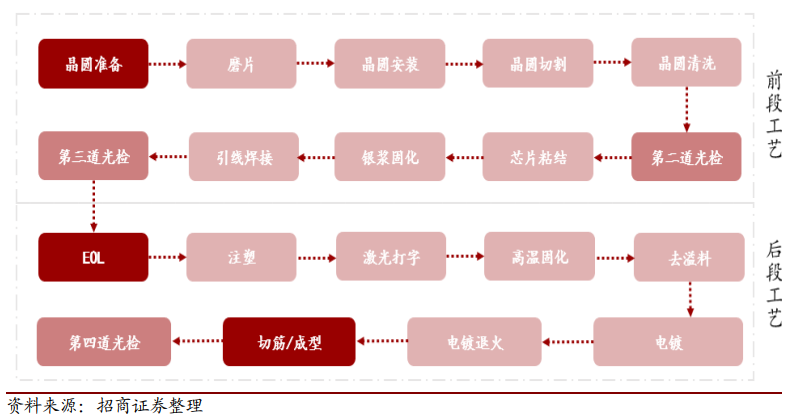

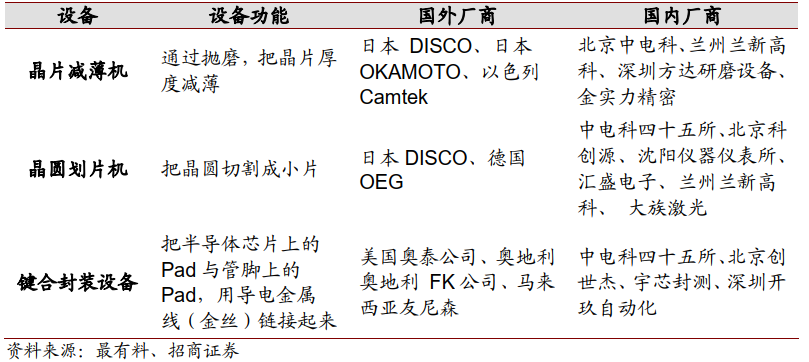

经过晶圆中测后,进入装配和封装步骤,以便把单个芯片包装在一个保护管壳内。硅片背面进行研磨以减少衬底的厚度。 一片厚的塑料膜被贴在每个硅片的背面,然后在正面沿着划片线用带划片刀将每个硅片上的芯片分开。在装配厂,芯片被压焊或抽空形成装配包,利用塑料或陶瓷包装晶粒与引线以成集成电路(目的是为了制造出所生产的电路的保护层,避免电路受到机械性刮伤或是高温破坏)。经过晶片切割——焊线——封胶——剪切/成形,完成封装,先进封装技术包括 3D、 TSV(穿硅通孔)、 FOWLP(扇出晶圆级封装)和倒装芯片。最后进行芯片终测,为确保芯片的功能,要对每一个被封装的集成电路进行测试,包括结构检测、光罩检测等,以满足制造商的电学和环境特性参数要求。

图23:晶圆封测工序

测试往往在封装工厂进行,因而封装和测试常常被当做整体的封测行业。封测环节的市场集中度较高,截止 2019Q1 全球前十大的封测企业市场份额约为 83%。主要包括各大 IDM 公司和专业代工封测厂商,份额各占 50%。比较大型的封测厂商有日月光、安靠、力成等,内地为长电科技、华天科技和通富微电等。

封测环节是我国最早进入半导体的切入口,因而也是我国半导体产业链中发展最成熟的环节,增长稳定,属于率先突破的行业。 自 2012 年以来,我国集成电路封装测试业一直持续保持两位数增长。 2018 年我国集成电路封装测试业的销售规模为 2194 亿元,同比增长 16%。我国大陆在全球半导体封装测试产业领域的销售规模仅次于中国台湾,封测产值占全球比例超过 16%,是第三大封测市场。而通过收购星科金朋,长电科技拥有了 WLSCP(晶圆级封装)、 SiP(系统级封装)、 PoP(堆叠封装)的高端先进封装技术,已经发展了高通、博通、闪迪、 Marvell 等国际高端客户。

半导体检测设备分为过程工艺控制检测和后道测试环节(ATE),前者主要包括结构检测、光罩检测、缺陷检测、电阻检测、离子浓度检测等前道检测,后者主要包括封装前的中测以及封装后的测试( FT)。 过程工艺控制检测的企业主要有 KLA-TENCOR、应用材料和日立三家公司, CR3 不低于 70%。后道工序检测主要有泰瑞达、爱德万和Xcerra 垄断, CR3 接近 90%,国产厂商包括长川科技,精测电子以及华兴源创等。

半导体的封测环节设备投入占设备总投入比例约为 15%, 预计 2019 年我国封测设备的市场空间为 176 亿元,其中封装和测试的比例各占一半左右。

图24:封装设备概况

图25:测试设备概况

4、检查设备

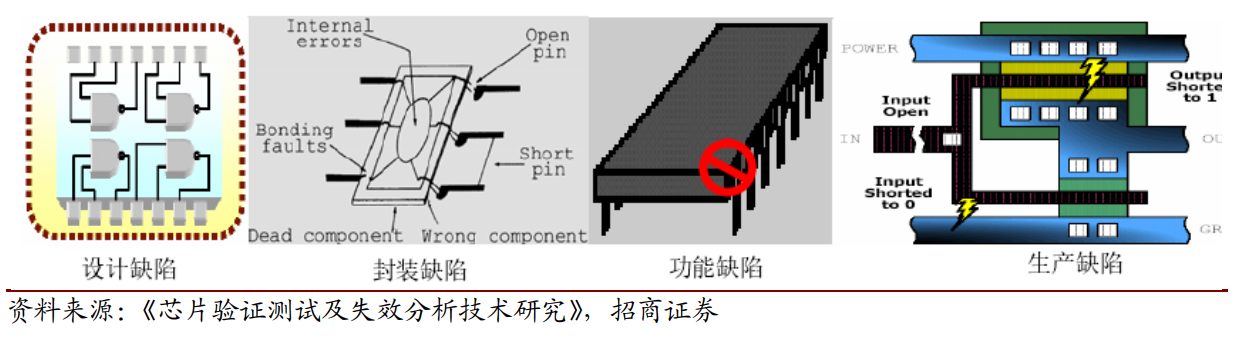

缺陷贯穿生产过程,未及时修正则导致最终失效。 集成电路的设计、加工、制造以及生产过程中,各种各样人为、非人为因素导致错误难以避免,造成的资源浪费、危险事故等代价更是难以估量。设计的漏洞、布局布线的失误、工作条件的差异、原料的纯度不足和存在缺陷以及机器设备的误操作等造成的错误,都是导致电路产生缺陷最终失效的原因。测试成为贯穿于集成电路设计、制造、生产中的、保证芯片质量的重要环节。

图26:集成电路缺陷示例

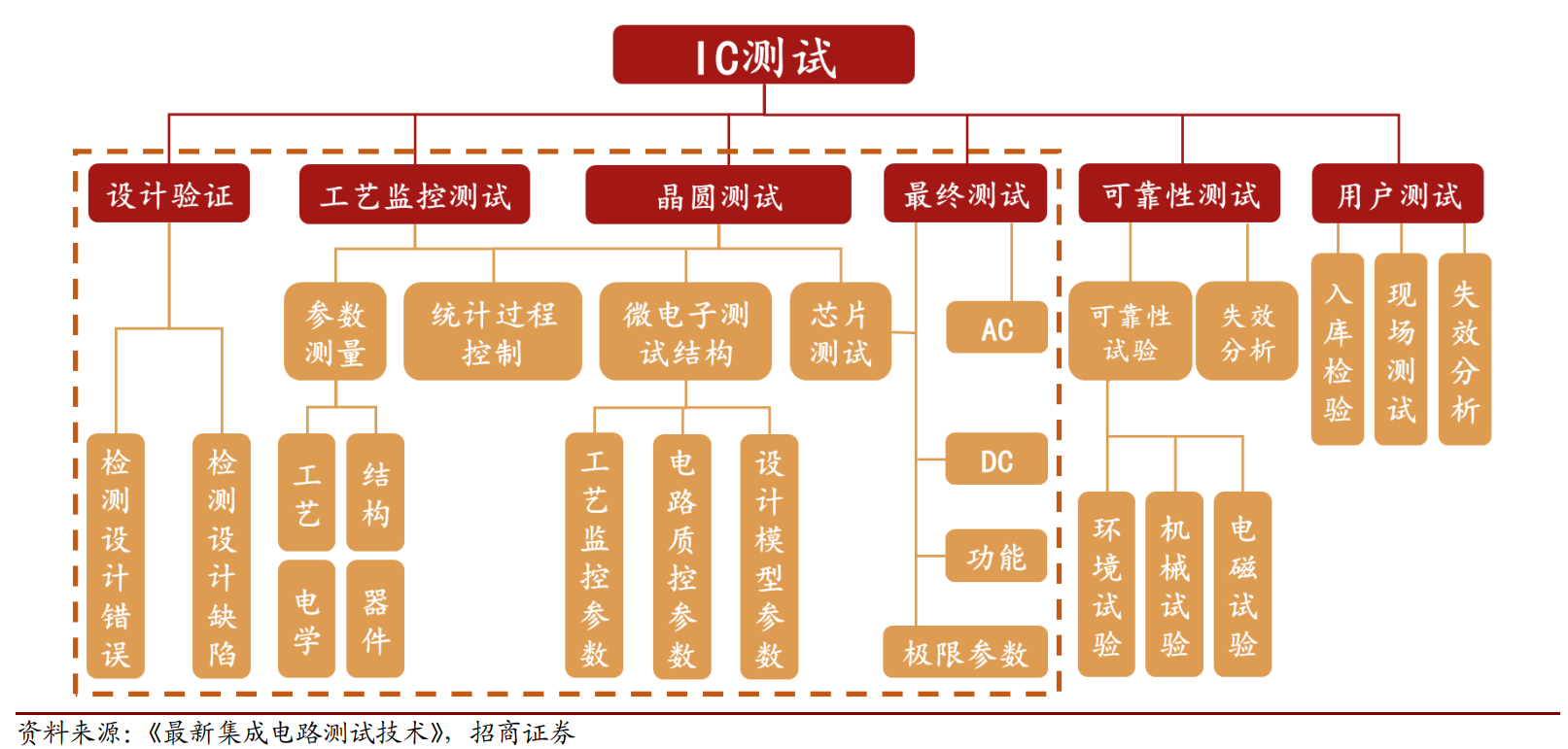

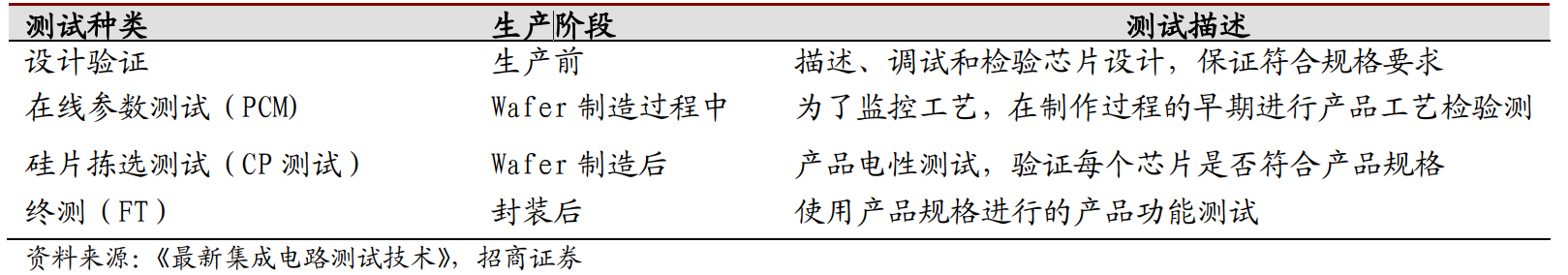

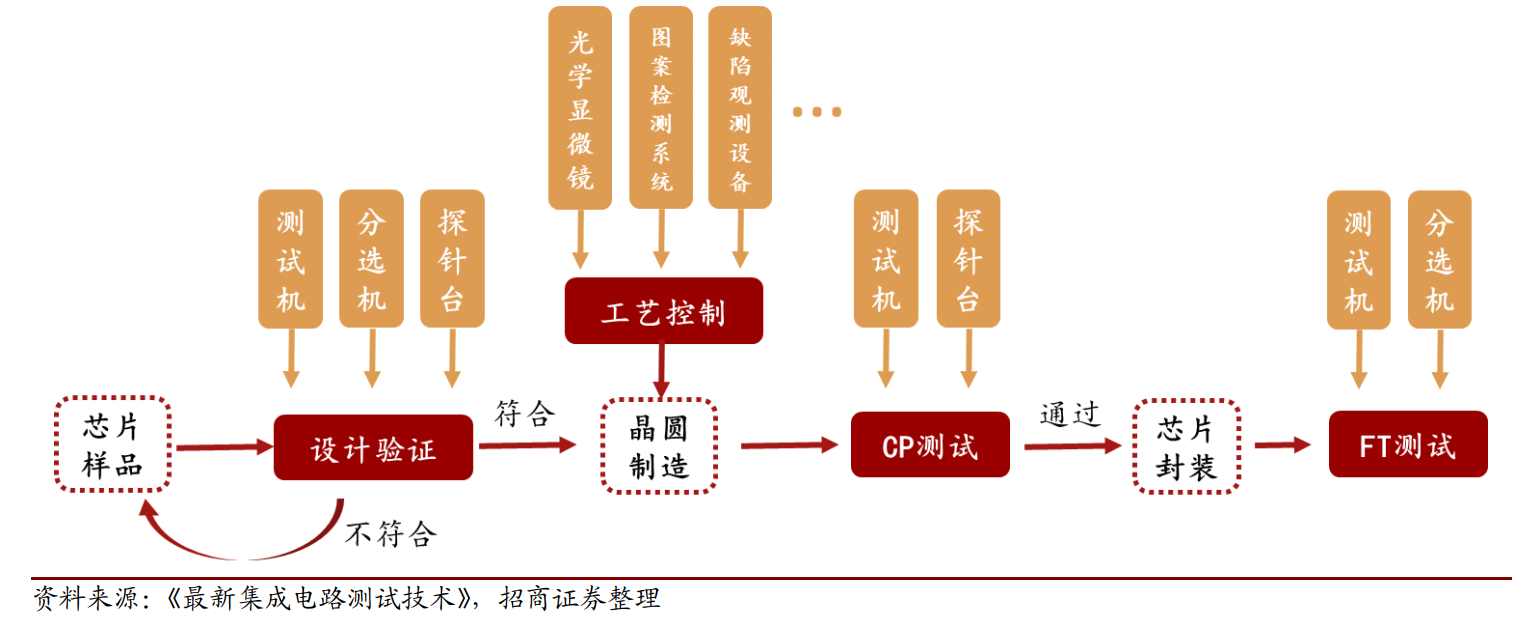

测试环节覆盖生产全过程,保证芯片符合规格。 以 IC 测试为例, IC 从设计到失效整个寿命中所经历的测试主要有设计验证、工艺监控测试、晶圆测试、最终测试、可靠性测试、用户测试。其中前四个发生在制造过程中,设计验证在批量生产前进行,最终测试在芯片封装后进行,所有测试目的是保证芯片符合规格,尽量避免损失升级。

图27:集成电路寿命全过程中各类测试框图

图28:生产过程中主流测试环节

4.1、设计验证

设计验证主要检测芯片样品功能设计,在生产前进行。 设计验证针对的是芯片样品,主要工作是检测芯片设计的功能是否能够达到客户要求,在检测过程中会对芯片样品逐一检查,只有通过设计验证的产品型号才会开始进入量产,由于其发生在芯片制造最早环节,性价比相对最高,可为芯片批量制造指明接下来的方向。

设计验证过程中需要使用全部半导体测试设备。 由于设计验证的特殊功能定位,其过程包括了整个芯片的制造流程,所需测试设备也包含了过程工艺检测过程中的光学设备等、晶圆检测中的探针台等以及最终检测过程中的分选机、测试机等。经过设计验证的产品型号才会开始进入量产。

图29:芯片测试及设备流程图

4.2、过程工艺检测

顾名思义, 过程工艺控制应用于晶圆制造的全过程。 在晶圆的制造过程中,包括离子注入、抛光、刻蚀等几乎任意一个环节都会由于技术不精确或外在环境污染等而形成缺陷,从而导致芯片最终失效。 主要检测的指标包括膜厚、表面缺陷、关键尺寸等。 例如整个晶圆的制造工艺便是不断的成膜工艺,在硅片表面形成不同的膜,膜厚便是膜的关键质量参数,针对不同种类薄膜测试参数也不尽相同,例如对于不透明膜的测量便使用四探针来测量方块电阻来计算膜厚,针对透明膜便主要依据光学测试进行测量。

图30:生产过程中主流测试项

4.2.1、量测——判断厚度、应力等指标

硅片工艺是成膜工艺。 集成电路的主体结构和器件都是由各种形状和尺寸的膜构成的,它们或是透明的膜或是不透明的膜,类型有金属、绝缘体、光刻胶和多晶硅,薄膜厚度的任何微小变化,对集成电路的性能都会产生直接的影响。除此之外,薄膜材料的力学性能,透光性能,磁性能,热导率,表面结构等都与厚度有着密切的联系,因此薄膜厚度的精准是是高成品率制造工艺的基础。

椭偏仪—测量透明椭偏仪—半透明薄膜厚度最精确的方法之一。由于具有非接触性、非破坏性、测量精度高和适于测量较薄膜层的特点,成为了半导体工业常用的薄膜测量工具。 当一束光射到薄膜面上时,在上界面和下界面形成多次反射和折射,形成椭圆偏振光。通过测量得到的椭圆偏振光的偏振态(幅度和相位),并根据已知的输入值(例如反射角、入射光的偏振态),则可精确地确定薄膜的厚度。椭偏仪测试具有小的测试点、图形识别软件和高精度硅片定位的优势,但由于其是一种光学测量方法,无法测量不透明薄膜的厚度。椭偏仪可测量的材料包括金属、涂覆聚合物和金属。 其中只有薄的金属才可以被看做半透膜,如铜互连工艺中用到的铜种子层,厚度大于 1000A 的金属层通常被认为是不透明的,不能用椭偏仪测量。椭偏仪可以直接集成到工艺设备中,应用于注入刻蚀和平坦化一些领域的原位(实时)测试。

椭偏仪 2013 年全球市场规模为 4086 万美元,销售量 1018 台,据预测 2023 年市场规模将达到 8582 万美元,销售量 2844 台。行业已经发展成熟且高度集中, .A.Woollam,Horiba, Semilab, Sentech, Angstrom Sun Technologies 占据了大部分市场份额,并在全球市场中发挥重要作用。国内椭偏仪的龙头企业是北京量拓科技,公司在太阳能电池检测椭偏仪取得一定成绩,但在芯片检测方面还与国际水平存在一定差距。

不透明导电薄膜可用四探针法来测量。 其原理是用四个等距的金属探针接触硅表面,外边的两令探针通直流电流 I,中间两个探针之间的电压降 V 由电位差计测量。由所测得的电流 I 和电压 V,利用关于样品和探针几何结构的适当校正因子,可以直接换算成薄层电阻,最后根据材料的电阻率换算出薄膜厚度。

检查膜应力可使用原子力显微镜(AFM)或扫描电子显微镜(SEM),其中 SEM 是目前最广泛使用的表面形貌仪。 SEM 利用二次电子信号成像来观察样品的表面形态:当高能电子束轰击样品表面时,入射电子束与样品间的相互作用, 99%以上的入射电子能量将转变成热能,其余约 1%的入射电子能量将从样品中激发出各种有用的信息,检测仪器将其转变为放大的电信号,并在记录仪上显示出来。

SEM 市场主要被美国、日本、德国所瓜分,进口依赖严重。 日本日立、日本电子公司、美国 FEI 以及德国蔡司构成 SEM 全球市场的几大巨头,我国 SEM 严重依赖进口,